www.datasheet4u.com

# OneNAND™MCP SPECIFICATION

| NAND Density | Part No.          | Vcc_core         | Vcc_IO           | PKG        |

|--------------|-------------------|------------------|------------------|------------|

| 256Mb NAND   | T.B.D             | 1.8V(1.7V~1.95V) | 1.8V(1.7V~1.95V) | T.B.D      |

|              | KEF00F0000CM-EG00 | 2.6V(2.4V~2.8V)  | 2.6V(2.4V~2.8V)  | 63FBGA(LF) |

|              | KEF00F0000CM-SG00 |                  |                  | 63FBGA     |

| 512Mb NAND   | KEC00C00CM-EGG0   | 1.8V(1.7V~1.95V) | 1.8V(1.7V~1.95V) | 63FBGA(LF) |

|              | KEC00C00CM-SGG0   |                  |                  | 63FBGA     |

|              | T.B.D             | 2.6V(2.4V~2.8V)  | 2.6V(2.4V~2.8V)  | T.B.D      |

Version: Ver. 0.0 Date: April 4, 2003

1

### **FLASH MEMORY**

#### **1. FEATURES**

#### ♦ Architecture

www.datas Design Technology: 0.25µm

- Voltage Supply

- Main: 1.8V device(1.7V~1.95V)

- 2.6V device(2.4V~2.8V)

- Host Interface & NAND Flash Interface: 1.8V device(1.7V~1.95V) 2.6V device(2.4V~2.8V)

- Organization

- Host Interface:16bit

- Internal BufferRAM

- BootRAM at booting, Cache-like at normal operation

#### Performance

- Host Interface type

- Synchronous Random Read

- : Clock Frequency: up to 45MHz @30pF

- Synchronous Burst Read

- : Clock Frequency: up to 45MHz @30pF

- : Burst Length: 4 words/ 8 words/ 16 words/ 32 words/ Continuous Linear Burst(2K words)

- Asynchronous Random Read

- Asynchronous Page Read: 4words

- Asynchronous Random Write

- Programmable Read latency

- 2Bit EDC / 1Bit ECC

- Multiple Reset

- Cold Reset / Warm Reset / Hot Reset

- Internal Bootloader

- Itelligent Data Protection

- Unique ID

- Detail information can be obtained by contact with Samsung

#### Software

- Handshaking Feature

- Interface Chip ID Read

- Detailed chip information by additional controller ID register

#### Packaging

- Package

- 63ball, 9.5mm x 12mm x max 1.4mmt FBGA

### **FLASH MEMORY**

#### 2. GENERAL DESCRIPTION

OneNAND<sup>™</sup> (MCP of NAND Flash Interface chip and NAND Flash) allows standard NAND Flash chips to interface with OneNAND<sup>™</sup> bus without performance penalty. This device is 1.8V/2.6V operation and comprised of about 10,000 gates and 4KB internal Buffer-

This 4KB BufferRAM is used as bootRAM during cold reset, and is used as cache RAM after cold reset. The operating clock frequency is up to 45MHz. This device is X16 interface with Host and X8 interface with NAND Flash. (Notice, in this specification, address is expressed by the byte order)

Also this device has the speed of ~40ns random access time. Actually, it is accessible with minimum 3clock latency(host-driven clock for synchronous read), but this device adopts the appropriate wait cycles by programmable read latency. OneNAND<sup>TM</sup> provides the multiple page read operation by assigning the number of pages to be read in the page counter register. The device is offered in the single type of package; 63ball, 9.5mm x 12mm x max 1.4mmt FBGA. The device includes one block sized OTP(One Time Programmable), which can be used to increase system security or to provide identification capabilities.

#### **3. PIN DESCRIPTION**

| Pin Name       | Туре | Nameand Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A11~A0         | I    | Address Inputs - Inputs for addresses during read operation, which are for addressing BufferRAM & Register.                                                                                                                                                                                                                                                                                                                                                                                |

| INT            | 0    | Interrupt<br>Notifyin Host when a command has completed. CMOS type driver output.                                                                                                                                                                                                                                                                                                                                                                                                          |

| DQ15~DQ0       | I/O  | Data Inputs/Outputs           - Inputs data during program and commands during all operations, outputs data during memory arra register read cycles.           Data pins float to high-impedance when the chip is deselected or outputs aredisabled.                                                                                                                                                                                                                                       |

| CLK            | I    | <b>Clock</b><br>CLK synchronizes the device to the system bus <u>freq</u> uency in synchronous read mode.<br>The first rising edge of CLK in conjunction with AVD low latches address input.                                                                                                                                                                                                                                                                                               |

| WE             | I    | $\frac{\textbf{Write Enable}}{WE}$ controls writes to the bufferRAM and registers. Datas are latched on the WE pulse's rising edge                                                                                                                                                                                                                                                                                                                                                         |

| AVD            | I    | Address Valid Detect         Indicates valid address presence on address inputs. During asynchronous read operation, all addresses are transparent during AVD's low, and during synchronous read operation, all addresses a latched on CLK's rising edge while AVD is held low for one clock cycle.         >Low: for asynchronous mode, indicates valid address: for vurst mode, causes starting address to ve latched on rising edge on CLK         >High: device ignores address inputs |

| RP             | I    | Reset Pin<br>When low, RP resets internal operation of OneNAND <sup>™</sup> . RP status is don't care during power-up<br>and bootloading.                                                                                                                                                                                                                                                                                                                                                  |

| CE             | I    | Chip Enable<br>CE-low activates internal controll logic, and CE-high deselects the device, places it in standby state,<br>and places A/DQ in Hi-Z                                                                                                                                                                                                                                                                                                                                          |

| OE             | I    | Output Enable<br>OE-low enables the device's output data buffers during a read cycle.                                                                                                                                                                                                                                                                                                                                                                                                      |

| UID            |      | <b>UID</b><br>The device is set to access Unique ID from NAND when this is high.<br>This should be low in normal operation.                                                                                                                                                                                                                                                                                                                                                                |

| Power Supply   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Vcc            |      | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Vss-Core       |      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| etc            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RFU            |      | Reserved for future use<br>RFU1 reserved for A12. RFU2 is reserved for A15. RFU3 is reserved for A14. RFU4 is reserved for A                                                                                                                                                                                                                                                                                                                                                               |

| DNU            |      | Do Not Use<br>Leave it disconnected. These pins are used for testing.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC             |      | No Connection<br>Lead is not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

NOTE: Do not leave power supply(VCC, VSS) disconnected.

### **FLASH MEMORY**

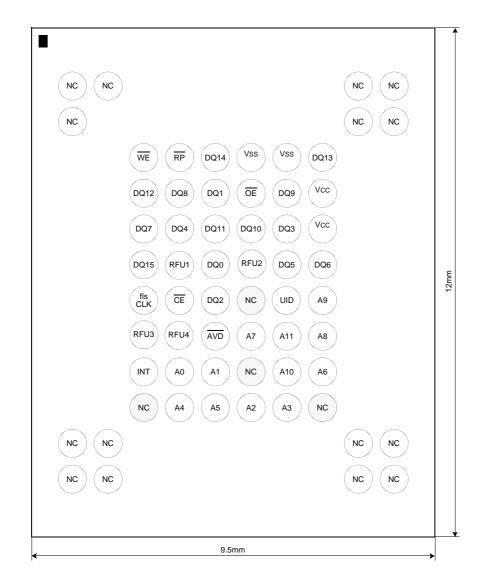

### 4. PIN CONFIGURATION

www.datasheet4u.com

(TOP VIEW, Balls Facing Down) 63ball FBGA OneNAND<sup>™</sup> Chip 9.5mm x 12mm x max. 1.4mmt, Ball Pitch: 0.8mm

### **FLASH MEMORY**

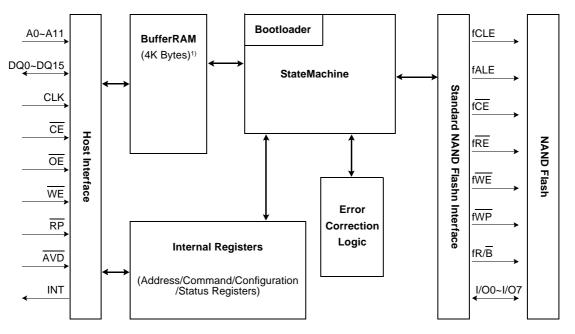

#### 5. BLOCK DIAGRAM For OneNAND™MCP

www.datasheet4u.com

- Host interface

- 4KB BufferRAM

- Command and status registers

- State Machine (Bootloader is included)

- Error Correction Logic

- Standard NAND flash Interface

- NAND Flash

NOTE:

At cold reset, bootloader copies boot code(4K byte size) from NAND Flash BufferRAM. and except cold reset host can use BufferRAM like cacheRAM.

### **FLASH MEMORY**

#### 6. ACCESSTIMINGS for OneNAND™ MCP

| I        | Operation                                                               | CE | OE | WE | A0~15   | DQ0~15     | RP | CLK | AVD |

|----------|-------------------------------------------------------------------------|----|----|----|---------|------------|----|-----|-----|

| www.data | sheet4u.corStandby                                                      | Н  | Х  | Х  | Х       | High-Z     | Н  | Х   | Х   |

|          | Warm Reset                                                              | Х  | Х  | Х  | Х       | High-Z     | L  | Х   | Х   |

|          | Asynchronous Write                                                      | L  | Н  | L  | Add. In | Data In    | Н  | х   |     |

|          | Asynchronous Read                                                       | L  | L  | н  | Add. In | Data Out   | н  | L   | or  |

|          | Load Initial Burst Address                                              | L  | Н  | н  | Add. In | х          | Н  | _   |     |

| Ť        | Burst Read                                                              | L  | L  | н  | x       | Burst Dout | Н  |     | or  |

|          | Terminate Burst Read<br>Cycle                                           | Н  | х  | Н  | х       | High-Z     | Н  | х   | х   |

|          | Terminate Burst Read<br>Cycle                                           | х  | х  | х  | х       | High-Z     | L  | х   | х   |

|          | Terminate Current Burst<br>Read Cycle and Srart<br>New Burst Read Cycle |    | Н  | Н  | Add In  | High-Z     | Н  |     |     |

X=Don't Care

www.datasheet4u.com

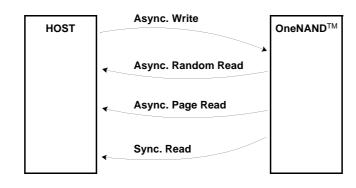

#### < BUS OPERATION >

#### < ACCESS TYPES >

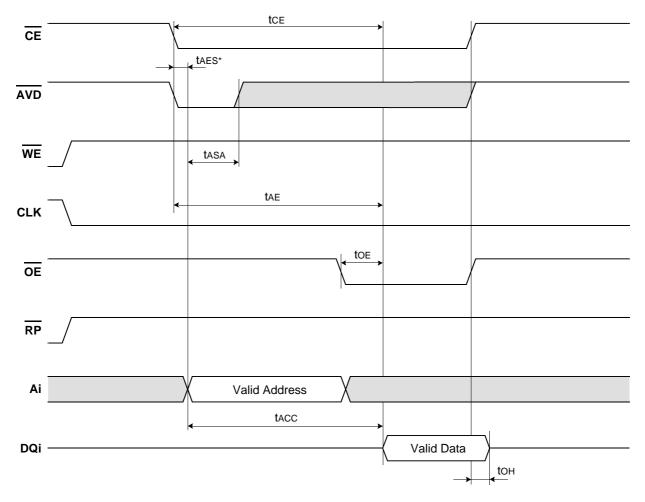

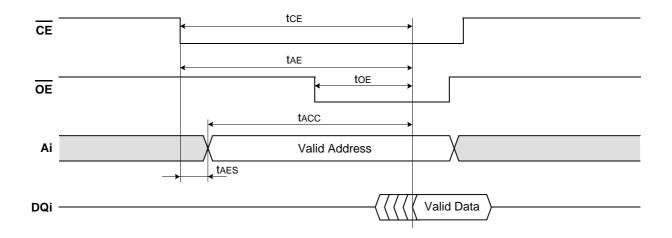

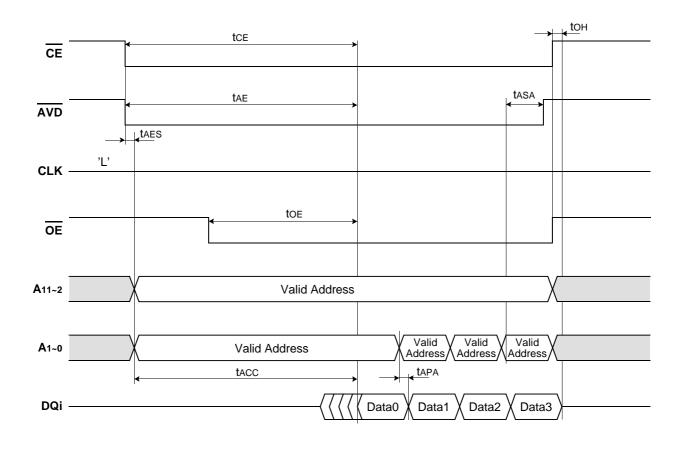

#### Figure 1. Asynchronous Read Mode

\* Please notice, tAES is Address delay from  $\overline{CE}$  &  $\overline{AVD}$ 's low, and tAES should not be over 10ns.

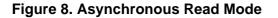

### Figure 2. Latched Asynchronous Read Mode

www.datasheet4u.com

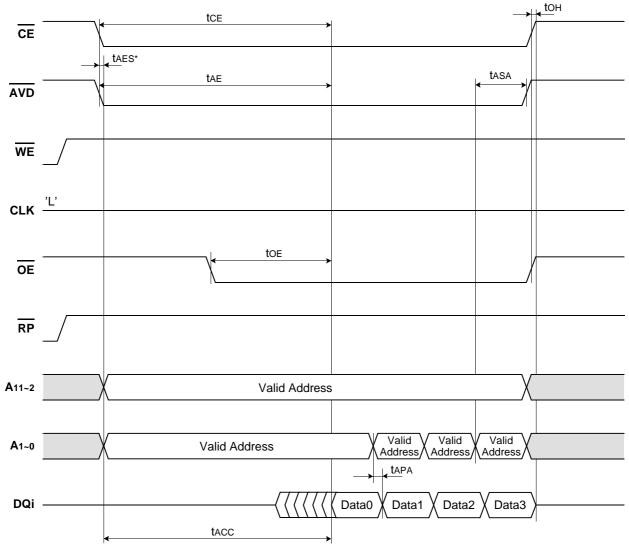

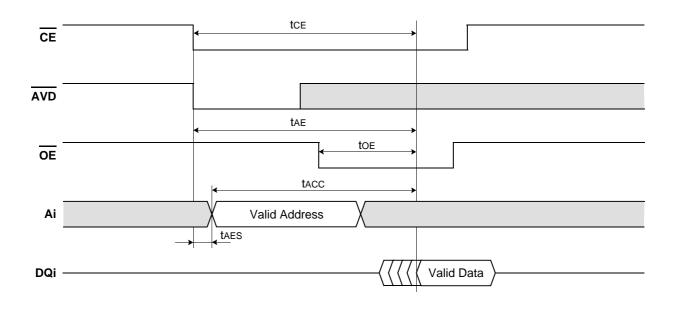

#### Figure 3. Asynchronous Page Read Mode

\* Please notice, tAES is Address delay from CE & AVD's low, and tAES should not be over 10ns.

www.datasheet4u.com

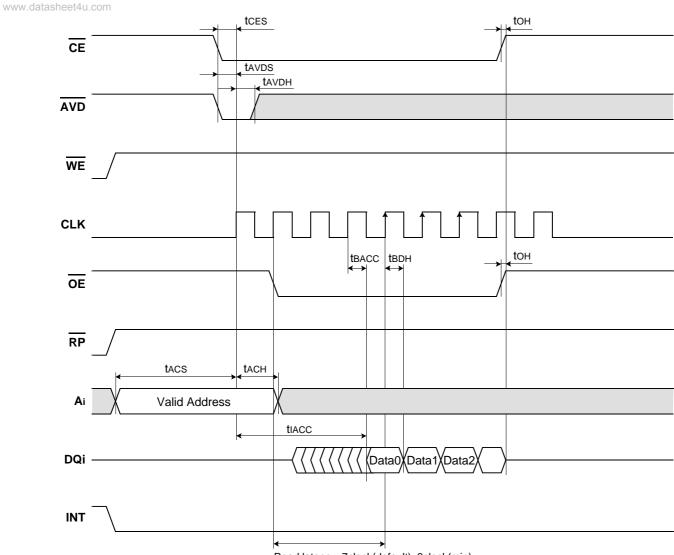

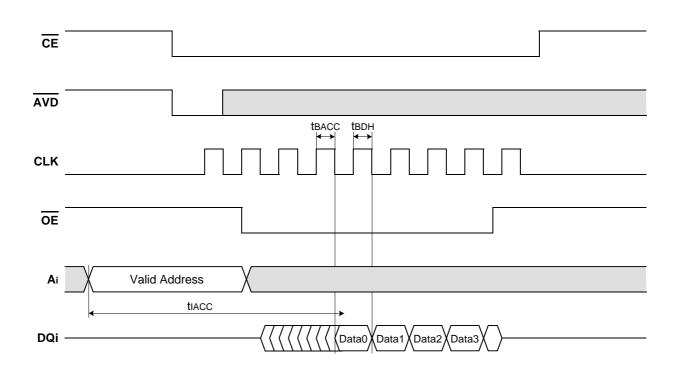

### Figure 4. Synchronous Burst Read Mode

Read latency: 7clock(default), 3clock(min)

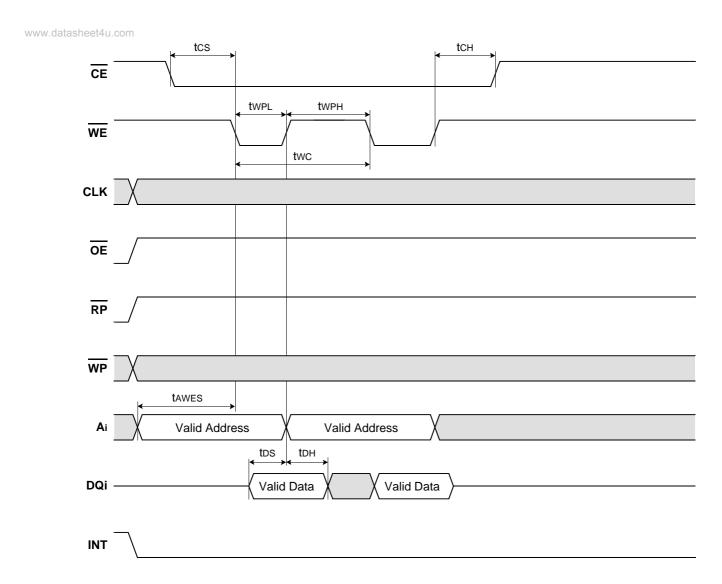

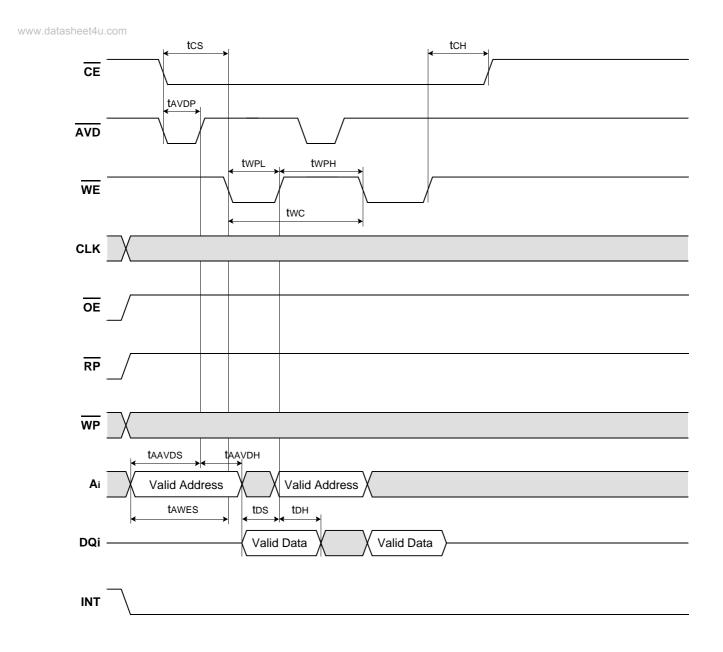

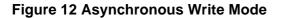

### Figure 5. Asynchronous Write Mode(No AVD pin case)

#### Figure 6. Latched Asynchronous Write Mode

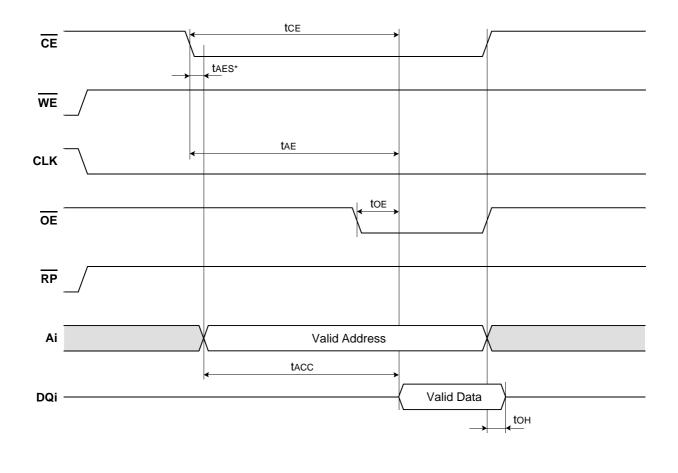

#### Timing Diagram for OneNAND™

The read cycle is initiated by first applying address to the address bus. The address latch is transparent while  $\overline{CE}$  is low. The random access time is measured from a stable address, falling edge of  $\overline{CE}$ . The clock should remain "0" during asynchronous access. www.dataAddress access time(tACC) is equal to the delay from stable addresses to valid output data. The chip enable access time(tCE) is the delay from the stable addresses and stable  $\overline{CE}$  to valid data at the outputs. The output enable access time(tOE) is the delay from the falling edge of  $\overline{OE}$  to valid data at the output.  $\overline{CE}$  must toggle in asynchronous read operation.

#### Figure 7. Asynchronous Read Mode

# **FLASH MEMORY**

#### Lathced Asynchronous Read Operation

The read cycle is initiated by first applying address to the address bus. The address latch is transparent while AVD is low. The random access time is measured from a stable address, falling edge of AVD or falling edge of CE which ever occurs last. The clock www.datashould/remain "0" during asynchronous access. Address access time(tACC) is equal to the delay from stable addresses to valid output data. The chip enable access time(tCE) is the delay from the stable addresses and stable CE to valid data at the outputs. The output enable access time(tOE) is the delay from the falling edge of OE to valid data at the output. CE and AVD must toggle in asynchromous read operation.

### **FLASH MEMORY**

#### **Asynchronous Page Read Operation**

Asynchronous page read mode is the default state and provides a high data transfer rate for non clocked memory subsystems. The page size is four words, and A1~0 addresses one of the four words. The read cycle is initiated by first applying address to the www.dataaddress.bust. The address latch is transparent while AVD is low. The address is latched by internal address latch circuit. The random access time is measured from a stable address, falling edge of AVD or falling edge of CE which ever occurs last. The clock should remain "1" during asynchronous access. Address access time(tACC) is equal to the delay from stable addresses to valid output data. The chip enable access time(tCE) is the delay from the stable addresses and stable CE to valid data at the outputs. The output enable access time(tOE) is the delay from the falling edge of OE to valid data at the output. CE and AVD must toggle in asynchromous read operation.

#### Figure 9. Asynchronous Page Read Mode

# **FLASH MEMORY**

#### **Synchronous Burst Read Operation**

When the device is powered up, it defaults to asynchronous read operation. Burst mode is selected by System Configuration register bit 15. The burst mode is used to improve the data transfer between the memory and the system processor. The burst mode is used www.datamiy/for read operations. Burst length is available on 4words/ 8words/ 16words/ 32words/ Continuous length, and is set by BL of System configuration reguster. The Bus Controller in the system will insert required read latency to meet host random access time. The first access time in the burst is equal to the random access time. In the burst access, the address is latched at the rising edge of the clock pulse when AVD is low. The first data in the burst access is available after the random access time. The Bus Controller reads data at the first rising edge of the clock after read latency. There is no conflict between AVD's low and OE's low.

The output buffers need to settle before the first data is available. Due to this, the shortest random access is at least one clock cycles from the rising edge of the clock when  $\overline{\text{AVD}}$  is low. This is defined as random access without any wait state. As the random access is allowed to be much longer than one clock cycles, the flash device has to support wait state insertion in order to synchronize the start of the burst access.

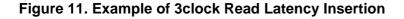

#### Figure 10. Synchronous Burst Read Mode(3clock read latency case)

#### **Programmable Read Latency**

The programmable read latency value indicates to the device the number of additional clock cycles that must elapse after AVD is driven active before data will be available.

www.dataThe number of read latency that should be programmed into the device is directly related to the clock frequency. Upon Power up, the device defaults to seven cycles. The total number of the read latency is programmable from zero to seven cycles. A hardware reset will set read latency to seven cycles after power-up. The minimum read latency for this device is three cycle assuming 40MHz system clock.

#### **Asynchronous Write Operation**

Write is allowed only in the asynchronous mode. The address is latched at the rising edge of the CE signal. The random access time is measured from a stable address, falling edge of CE. Write operations are asynchronous. Therefore, CLK is ignored during write www.dataoperation. There is no conflict between CE's low and OE's low.

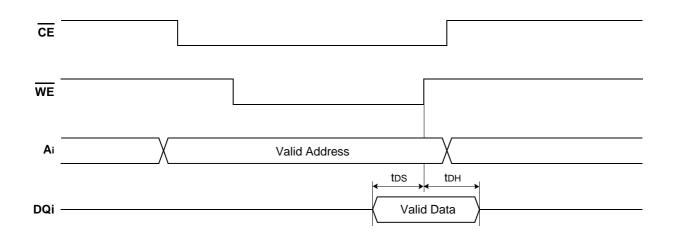

#### Latched Asynchronous Write Operation

At Latched Asynchronous Write operation, the address is latched at the rising edge of the AVD signal. Because Write operations are asynchronous operation, CLK is ignored during write operation. There is no conflict between AVD's low and OE's low. www.datasheet4u.com

#### Figure 13. Latched Asynchronous Write Mode

### 7. Electrical Specifications

### 7-1. Absolute Maximum Ratings

| www.data | asheet4u.com Param | eter           | Symbol     | Rating | Unit |

|----------|--------------------|----------------|------------|--------|------|

|          | Voltage on any pin | Vcc            | Vcc        | 3.6    | V    |

|          | relative to Vss    | All other pins | VIN        | 3.6    |      |

|          | Latch-up           | current        | llatch     | ±200   | mA   |

|          | Storage ten        | Тѕтс           | -65 to 150 | °C     |      |

#### NOTE:

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### 7-2 Recommended Operating Ratings 7-2-1. Supply Voltage(Voltage reference to GND)

| Parameter | Symbol |     | 1.8V Part |      |     | 2.6V Part |     | Unit |

|-----------|--------|-----|-----------|------|-----|-----------|-----|------|

| Parameter | Symbol | Min | Тур.      | Max  | Min | Тур.      | Max | Unit |

| Supply    | Vcc    | 1.7 | 1.8       | 1.95 | 2.4 | 2.6       | 2.8 | V    |

| Voltage   | Vss    | 0   | 0         | 0    | 0   | 0         | 0   | V    |

#### 7-2-2. Temperature

| Parameter              | Symbol               | Rating    | Unit |

|------------------------|----------------------|-----------|------|

| Commercial temperature | TA(Commercial temp.) | 0 to 70   | °C   |

| Industrial temperature | TA(Industrial temp.) | -25 to 85 | Ů    |

# **FLASH MEMORY**

### 7-3. DC Characteristics

| Denementar                      | Complete | Test Candition                                            | 1.8V Part   |      |             |             | 2.6V Par | t           | Unit |

|---------------------------------|----------|-----------------------------------------------------------|-------------|------|-------------|-------------|----------|-------------|------|

| Parameter<br>asheet4u.com       | Symbol   | Test Condition                                            | Min         | Тур. | Max         | Min         | Тур.     | Max         | Unit |

| Input leakage current           | lu       | VIN=Vss to Vcc<br>Vcc=Vcc(max)                            | -7          | -    | 7           | -10         | -        | 10          |      |

| Output leakage current          | ILO      | Vout=Vss to Vcc<br>Vcc=Vcc(max)                           | -7          | -    | 7           | -10         | -        | 10          | uA   |

| Standby current                 | Iccs     | <u>Vcc=Vc</u> c(max)<br>CE=RP=VIн<br>INT=floating         | -           | 22   | 85          |             | 22       | 85          | -    |

| Active Async.<br>Read Current   | ICCR1    | VIN=VIH or VIL<br>CE=VIL<br>OE=VIH                        | -           | 10   | 20          |             | 10       | 25          |      |

| Active Sync.<br>Read Current    | ICCR2    | <u>CE</u> =VIL<br>OE=VIн<br>Continuous Burst<br>CLK=45Mhz | -           | 11   | 20          |             | 11       | 25          | mA   |

| Active Program<br>Current       | Iccw     | Program in<br>Progress                                    | -           | 12   | 20          |             | 12       | 25          |      |

| Active Erase<br>Current         | ICCE     | Erase in Progress                                         | -           | 12   | 20          |             | 12       | 25          |      |

| Input High<br>voltage           | Viн      | -                                                         | Vcc<br>-0.4 | -    | Vcc+<br>0.4 | Vcc-<br>0.4 | -        | Vcc+<br>0.4 |      |

| Input Low voltage               | VIL      | -                                                         | -0.5        | -    | 0.4         | -0.5        | -        | 0.4         |      |

| High level output voltage       | Vон      | Iон=-100uA<br>Vcc=Vcc(min)                                | Vcc-<br>0.2 | -    | -           | Vcc-<br>0.2 | -        | -           | V    |

| Low level output<br>voltage     | Vol      | Iон=-100uA<br>Vcc=Vcc(min)                                | -           | -    | 0.2         | -           | -        | 0.2         |      |

| Input capacitance <sup>1)</sup> | CIN      | Any input and<br>Bi-directional buffers                   | -           | -    | 10          | -           | -        | 10          | pF   |

| Output capacitance1)            | Соит     | Any output buffers                                        | -           | -    | 10          | -           | -        | 10          |      |

**NOTE:** 1. This value excludes package parasitic

# **FLASH MEMORY**

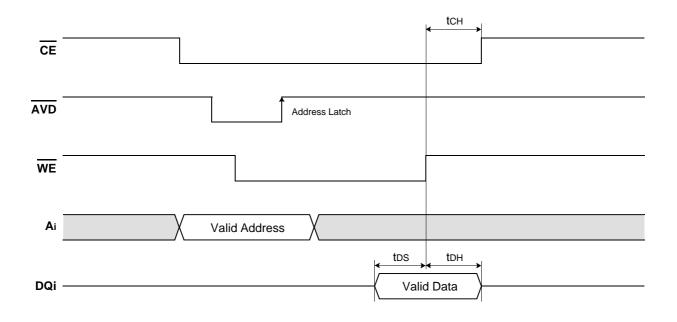

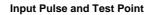

#### 7-4. AC Test Condition

| Parameter                              | Value     |

|----------------------------------------|-----------|

| www.datasheet4u.com Input Palse Levels | 0V to Vcc |

| Input Rise and Fall Times              | 5ns       |

| Input and Output Timing Levels         | Vcc/2     |

| Output Load                            | CL=30pF   |

SAMSUNG ELECTRONICS

### **FLASH MEMORY**

### 7-5. AC Characteristics

### www.dat Asynchronous Read AC Parameters

| Parameter | Description                                                                        |     | 1.8V Part | t   |     | Unit |     |      |

|-----------|------------------------------------------------------------------------------------|-----|-----------|-----|-----|------|-----|------|

| Farameter | Description                                                                        | Min | Тур.      | Max | Min | Тур. | Max | Unit |

| tCE       | Access time from $\overline{CE}$ Low                                               | -   | -         | 55  | -   | -    | 55  | ns   |

| tOE       | Output Enable to Output Valid                                                      | -   | -         | 23  | -   | -    | 23  | ns   |

| tACC      | Asynchronous Access Time                                                           | -   | -         | 55  | -   | -    | 55  | ns   |

| tAE       | Random Access AVD-Data Valid                                                       | -   | -         | 55  | -   | -    | 55  | ns   |

| tOH       | Output hold from $\overline{CE}$ or $\overline{OE}$ change, whichever occurs first | 0   |           | 4   | 0   |      | 4   | ns   |

| tAPA      | Page address access time                                                           |     |           | 40  |     |      | 40  | ns   |

| tASA      | Address setup to AVD high                                                          | 7   |           | -   | 7   |      | -   | ns   |

| tAES      | CE & AVD setup to Valid Address                                                    | -   | -         | 10  | -   | -    | 10  | ns   |

| tCA       | CE setup to AVD falling edge                                                       | 0   | -         | -   | 0   | -    | -   | ns   |

### Asynchronous Read AC Parameters

| Denemater | Description                                              |     | 1.8V Par | t    |     | Unit |      |      |

|-----------|----------------------------------------------------------|-----|----------|------|-----|------|------|------|

| Parameter | Description                                              | Min | Тур.     | Max  | Min | Тур. | Мах  | Unit |

| tCES      | CE setup time to CLK                                     | 5   | -        | -    | 5   | -    | -    | ns   |

| tIACC     | Initial Access Time @45Mhz                               | -   | -        | 85.6 |     | -    | 84.6 | ns   |

| tBACC     | Burst Access Time<br>Valid clock to output delay         | -   | -        | 19   |     | -    | 17   | ns   |

| tBDH      | Data hold time from next clock cycle                     | 4   |          | -    | 4   | -    | -    | ns   |

| tAVDS     | AVD setup time to CLK                                    | 5   |          | -    | 5   | -    | -    | ns   |

| tAVDH     | AVD hold time to CLK                                     | 7   |          | -    | 8   | -    | -    | ns   |

| tACS      | Address setup time to CLK                                | 5   |          | -    | 5   | -    | -    | ns   |

| tACH      | Address hold time to CLK                                 | 7   |          | -    | 7   | -    | -    | ns   |

| tOH       | Output hold from CE or OE change, whichever occurs first | 4   |          | -    | 4   | -    | -    | ns   |

| tOE       | Output Enable ot Output Valid                            |     | 23       |      |     | 23   |      | ns   |

| tCLKH     | FIsCLK high time                                         | 10  |          |      | 10  |      |      | ns   |

| tCLKL     | FIsCLK low time                                          | 10  |          |      | 10  |      |      | ns   |

| tCA       | CE setup to AVD falling edge                             | 0   | -        | -    | 0   | -    | -    | ns   |

### **FLASH MEMORY**

### Write AC Parameters

| www.datash <b>Barame</b> | eter Description                |              | 1.8V Part | t   |     | 2.6V Part | :   | Unit |

|--------------------------|---------------------------------|--------------|-----------|-----|-----|-----------|-----|------|

| www.datashearame         | Description                     | Min          | Тур.      | Мах | Min | Тур.      | Max | Onit |

| tAVD                     | P AVD Low time                  | 12           |           | -   | 12  |           | -   | ns   |

| tAAVE                    | OS Asynchronous Address setup   | time 7       |           | -   | 7   |           | -   | ns   |

| tAWE                     | S Asynchronous Address setup    | to new low 5 |           |     | 5   |           |     |      |

| tAAVD                    | OH Asynchronous Address hold ti | me 7         |           | -   | 7   |           | -   | ns   |

| tDS                      | Data Setup Time                 | 5            |           | -   | 5   |           | -   | ns   |

| tDH                      | Data Hold Time                  | 4            |           | -   | 4   |           | -   | ns   |

| tWC                      | Write Cycle Time                | 80           |           | -   | 80  |           | -   | ns   |

| tWPL                     | Write Pulse Width Low           | 20           |           |     | 20  |           | -   | ns   |

| tWPH                     | H Write Pulse Width High        | 50           |           |     | 50  |           | -   | ns   |

| tCS                      | CE setup time                   | 0            | -         |     | 0   | -         | -   | ns   |

| tCH                      | CE Hold Time                    | 4            |           |     | 4   |           | -   | ns   |

| tAWE                     | S Address setup to WE low       | 5            |           |     | 5   |           |     | ns   |

| tVLW                     | H AVD rising edge to WE rising  | edge 10      |           |     | 10  |           |     | ns   |

### **FLASH MEMORY**

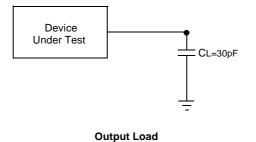

#### \*AVD connected case www.datasheet4u.com

> If host uses byte-order typed address, ADD<0> can be used as byte/word selection pin.

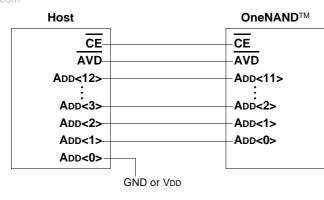

#### \*AVD disconnected case

> If host uses byte-order typed address, ADD<0> can be used as byte/word selection pin.

> In AVD disconnected case, AVD can be tled to CE or GND.